Your Fpga architecture design flow images are ready. Fpga architecture design flow are a topic that is being searched for and liked by netizens today. You can Get the Fpga architecture design flow files here. Download all royalty-free photos.

If you’re searching for fpga architecture design flow images information linked to the fpga architecture design flow keyword, you have visit the ideal site. Our website always gives you suggestions for refferencing the highest quality video and image content, please kindly search and find more enlightening video articles and images that match your interests.

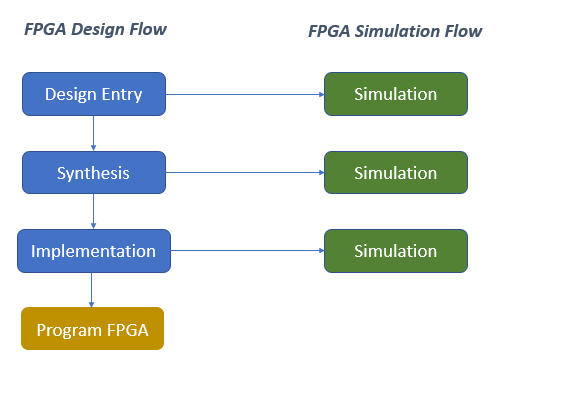

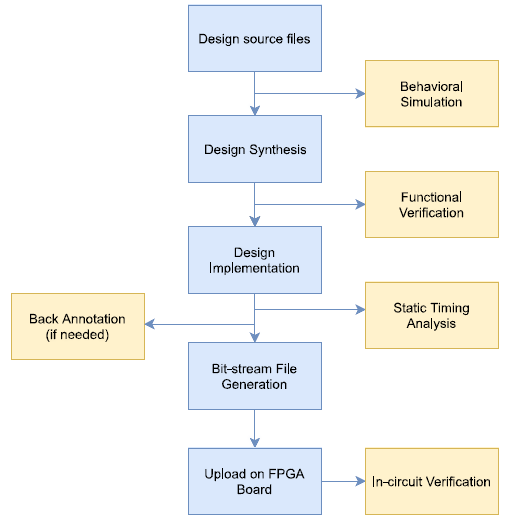

Fpga Architecture Design Flow. Generic Xilinx FPGA Architecture. FPGA vs ASIC. Describe the general Artix-7 FPGA architecture Understand the Vivado design flow Create and debug HDL designs Configure FPGA and verify hardware operation Configure FPGA architecture features such as Clock Manager using the Architecture Wizard Communicate design timing objectives through the use of Xilinx Design Constraints. This chapter discusses about the FPGA architecture design flow and the simulation using the FPGA.

Fpga Design Flow Overview Download Scientific Diagram From researchgate.net

Fpga Design Flow Overview Download Scientific Diagram From researchgate.net

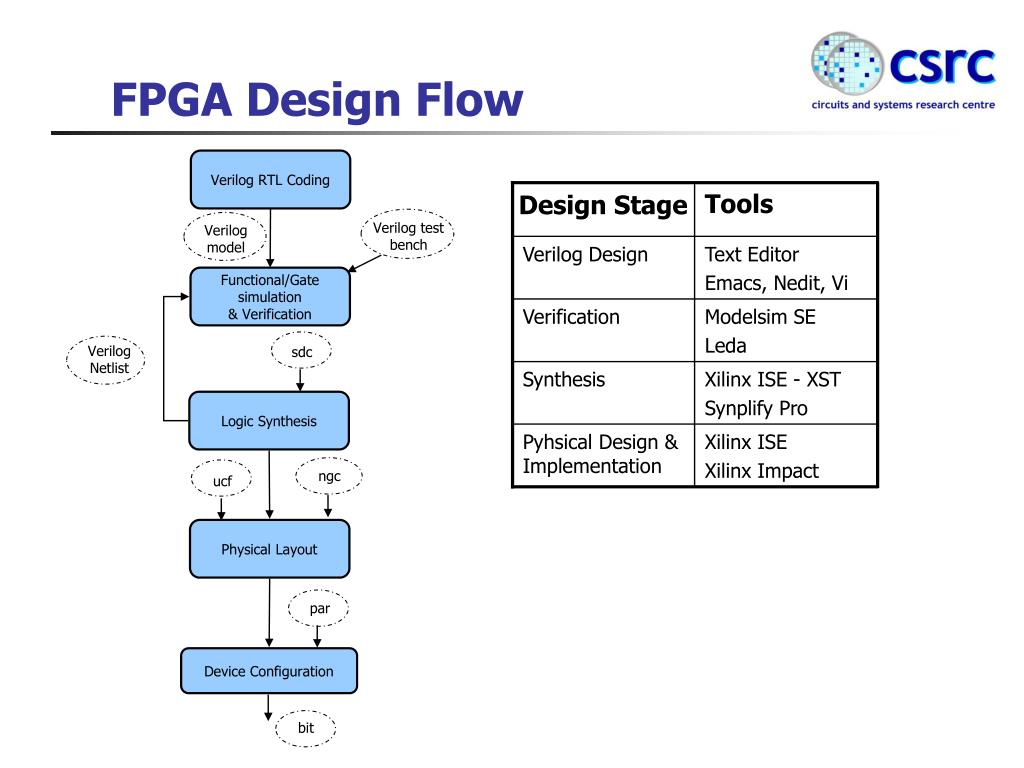

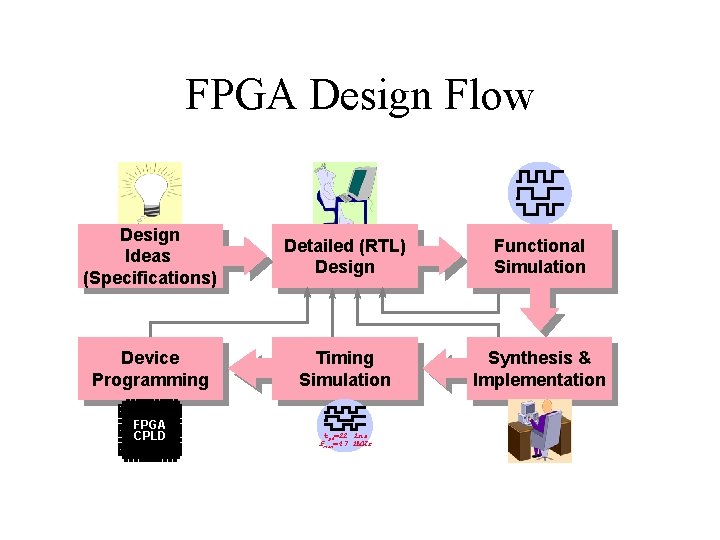

Field-programmable gate array FPGA is a device that has numerous gate switch arrays and can be programmed on-board through dedicated Joint Test Action. Programmable logic devices are used to realize the complex logic. The design flow will build a model of the specified FPGA architecture and map the given application onto it. More information can be found at Tutorials. FPGA course is a 6 months course provides in depth exposure to complete FPGA system design flow starting from RTL coding prototyping and validation. Design Entry Synthesis Implementation Bitstream Generation Simulation Complexity of HDL.

FFs multipliers adders using Odin II 60.

The design flow will build a model of the specified FPGA architecture and map the given application onto it. The design flow will build a model of the specified FPGA architecture and map the given application onto it. This is a preview of subscription content log in to check access. Example scripts can be found and ran under the examplesfpga directory. More information can be found at Tutorials. FPGA course is a 6 months course provides in depth exposure to complete FPGA system design flow starting from RTL coding prototyping and validation.

Source: hardwarebee.com

Source: hardwarebee.com

This is a preview of subscription content log in to check access. FPGA Design Flow - from HDL to physical implementation - Victor Andrei Kirchhoff-Institut für Physik KIP Ruprecht-Karls-Universität Heidelberg 6th Detector Workshop of the Helmholtz Alliance Physics at the Terascale Mainz 26022013. FPGA vs ASIC. The next sections of this paper is about the design flow for an FPGA-based project. The final bitstream format depends on the used platform.

Source: digitaltagebuch.wordpress.com

Source: digitaltagebuch.wordpress.com

FFs multipliers adders using Odin II 60. The next sections of this paper is about the design flow for an FPGA-based project. FPGA Design Flow SymbiFlow is an end-to-end FPGA synthesis toolchain because of that it provides all the necessary tools to convert input Verilog design into a final bitstream. A step-by-step lowdown on the basic flow of FPGA designing for new design engineers – SR. The final sections of this paper discuss in detail the design simulation and testing issues that arise when designing an FPGA.

Source: wdc65xx.com

Source: wdc65xx.com

FPGA Design Flow Figure 1 depicts the primary five stages in the FPGA design process. Programmable logic devices are used to realize the complex logic. Generic Xilinx FPGA Architecture. FPGAs are also used as accelerators for CPU prototyping of ASIC designs and in Emulation. Describe the general Artix-7 FPGA architecture Understand the Vivado design flow Create and debug HDL designs Configure FPGA and verify hardware operation Configure FPGA architecture features such as Clock Manager using the Architecture Wizard Communicate design timing objectives through the use of Xilinx Design Constraints.

Source: hardwarebee.com

Source: hardwarebee.com

This is a preview of subscription content log in to check access. Schematic based Hardware Description Language and combination of both etc. Virtex FPGA family name. Selection of a method depends on the design and designer. It is simple to use however the whole synthesis and implementation process is not trivial.

Source: researchgate.net

Source: researchgate.net

Programmable logic devices are used to realize the complex logic. Standard cell based IC vs. FPGA_Design_FLOW Design Entry There are different techniques for design entry. FPGA Design Flow SymbiFlow is an end-to-end FPGA synthesis toolchain because of that it provides all the necessary tools to convert input Verilog design into a final bitstream. The final bitstream format depends on the used platform.

Source: researchgate.net

Source: researchgate.net

Example scripts can be found and ran under the examplesfpga directory. This chapter discusses about the FPGA architecture design flow and the simulation using the FPGA. Design using standard cells Standard cells come from library provider Many different choices for cell size delay leakage power Many EDA tools to automate this flow Shorter design time. FPGA Design Flow An FPGA Field Programmable Gate Arrays is a programmable chip used in various industry applications such as 4G5G Wireless systems Signal Processing Systems and Image Processing Systems. The final sections of this paper discuss in detail the design simulation and testing issues that arise when designing an FPGA.

Source: digitalsystemdesign.in

Source: digitalsystemdesign.in

You will learn the steps in the standard FPGA design flow how to use Intel Alteras Quartus Prime Development Suite to create a pipelined multiplier and how to verify the integrity of the design using the RTL Viewer and by simulation using ModelSim. Describe the general FPGA architectures and the design flow Configure FPGA architecture features such as DCM using the Architecture Wizard Communicate design timing objectives through the use of global timing constraints Pinpoint design bottlenecks using the reports Utilize synthesis options to improve performance. FFs multipliers adders using Odin II 60. The next sections of this paper is about the design flow for an FPGA-based project. This chapter discusses about the FPGA architecture design flow and the simulation using the FPGA.

Source: researchgate.net

Source: researchgate.net

Due to programmable features the modern high-density FPGAs are used to prototype the complex ASICs and SOCs. FFs multipliers adders using Odin II 60. Standard cell based IC vs. In Module 2 you will install and use sophisticated FPGA design tools to create an example design. Example scripts can be found and ran under the examplesfpga directory.

Source: researchgate.net

Source: researchgate.net

Describe the general Artix-7 FPGA architecture Understand the Vivado design flow Create and debug HDL designs Configure FPGA and verify hardware operation Configure FPGA architecture features such as Clock Manager using the Architecture Wizard Communicate design timing objectives through the use of Xilinx Design Constraints. FPGA Design Flow An Introduction The design flow of Field Programmable Gate Arrays or FPGAs consists of several steps that must work in unison for proper function. FPGAs are also used as accelerators for CPU prototyping of ASIC designs and in Emulation. Shabany ASI FPGA hip Design Course Outline Course Outline Introduction to ASICFPGA IC Design Integrated Circuits IC History. FPGA course is a 6 months course provides in depth exposure to complete FPGA system design flow starting from RTL coding prototyping and validation.

Source: hardwarebee.com

Source: hardwarebee.com

Shabany ASI FPGA hip Design Course Outline Course Outline Introduction to ASICFPGA IC Design Integrated Circuits IC History. As a hardware-based architecture the FPGA is an attractive processing solution because it can simultaneously provide a user-selected balance among critical tradeoffs of high performance and speed outstanding design-in flexibility including field programmability and. If the designer wants to deal more with Hardware then Schematic entry is the better choice. Describe the general Artix-7 FPGA architecture Understand the Vivado design flow Create and debug HDL designs Configure FPGA and verify hardware operation Configure FPGA architecture features such as Clock Manager using the Architecture Wizard Communicate design timing objectives through the use of Xilinx Design Constraints. Standard cell based IC vs.

Source: researchgate.net

Source: researchgate.net

Example scripts can be found and ran under the examplesfpga directory. The steps consist of the following. Five main FPGA development phases. You will learn the steps in the standard FPGA design flow how to use Intel Alteras Quartus Prime Development Suite to create a pipelined multiplier and how to verify the integrity of the design using the RTL Viewer and by simulation using ModelSim. Programmable logic devices are used to realize the complex logic.

Source: slideserve.com

Source: slideserve.com

FPGAs are also used as accelerators for CPU prototyping of ASIC designs and in Emulation. More information can be found at Tutorials. Describe the general FPGA architectures and the design flow Configure FPGA architecture features such as DCM using the Architecture Wizard Communicate design timing objectives through the use of global timing constraints Pinpoint design bottlenecks using the reports Utilize synthesis options to improve performance. The design flow proceeds in several stages. Virtex FPGA family name.

Source: researchgate.net

Source: researchgate.net

A step-by-step lowdown on the basic flow of FPGA designing for new design engineers – SR. FPGA Design Flow An FPGA Field Programmable Gate Arrays is a programmable chip used in various industry applications such as 4G5G Wireless systems Signal Processing Systems and Image Processing Systems. FPGA Design Flow An Introduction The design flow of Field Programmable Gate Arrays or FPGAs consists of several steps that must work in unison for proper function. FPGA Design Flow. This chapter discusses about the FPGA architecture design flow and the simulation using the FPGA.

Source: fpgakey.com

Source: fpgakey.com

FPGA course is a 6 months course provides in depth exposure to complete FPGA system design flow starting from RTL coding prototyping and validation. The final sections of this paper discuss in detail the design simulation and testing issues that arise when designing an FPGA. It is simple to use however the whole synthesis and implementation process is not trivial. In Module 2 you will install and use sophisticated FPGA design tools to create an example design. Generic Xilinx FPGA Architecture.

Source: newelectronics.co.uk

Source: newelectronics.co.uk

FPGA Design Flow - from HDL to physical implementation - Victor Andrei Kirchhoff-Institut für Physik KIP Ruprecht-Karls-Universität Heidelberg 6th Detector Workshop of the Helmholtz Alliance Physics at the Terascale Mainz 26022013. Generic Xilinx FPGA Architecture. Field-programmable gate array FPGA is a device that has numerous gate switch arrays and can be programmed on-board through dedicated Joint Test Action. The steps consist of the following. Shabany ASI FPGA hip Design Course Outline Course Outline Introduction to ASICFPGA IC Design Integrated Circuits IC History.

Source: slidetodoc.com

Source: slidetodoc.com

Due to programmable features the modern high-density FPGAs are used to prototype the complex ASICs and SOCs. Features and Specifications of FPGAs. FPGA Design Flow. In Module 2 you will install and use sophisticated FPGA design tools to create an example design. FPGA Design Flow Figure 1 depicts the primary five stages in the FPGA design process.

Source: youtube.com

Source: youtube.com

Custom design IC Standard cell based IC. The next sections of this paper is about the design flow for an FPGA-based project. Describe the general FPGA architectures and the design flow Configure FPGA architecture features such as DCM using the Architecture Wizard Communicate design timing objectives through the use of global timing constraints Pinpoint design bottlenecks using the reports Utilize synthesis options to improve performance. FPGA Design Flow - from HDL to physical implementation - Victor Andrei Kirchhoff-Institut für Physik KIP Ruprecht-Karls-Universität Heidelberg 6th Detector Workshop of the Helmholtz Alliance Physics at the Terascale Mainz 26022013. The steps consist of the following.

Source: researchgate.net

Source: researchgate.net

FPGA implementation by RTL mode as well as IP Mode. It is simple to use however the whole synthesis and implementation process is not trivial. The steps consist of the following. Describe the general FPGA architectures and the design flow Configure FPGA architecture features such as DCM using the Architecture Wizard Communicate design timing objectives through the use of global timing constraints Pinpoint design bottlenecks using the reports Utilize synthesis options to improve performance. The final sections of this paper discuss in detail the design simulation and testing issues that arise when designing an FPGA.

This site is an open community for users to do submittion their favorite wallpapers on the internet, all images or pictures in this website are for personal wallpaper use only, it is stricly prohibited to use this wallpaper for commercial purposes, if you are the author and find this image is shared without your permission, please kindly raise a DMCA report to Us.

If you find this site helpful, please support us by sharing this posts to your preference social media accounts like Facebook, Instagram and so on or you can also bookmark this blog page with the title fpga architecture design flow by using Ctrl + D for devices a laptop with a Windows operating system or Command + D for laptops with an Apple operating system. If you use a smartphone, you can also use the drawer menu of the browser you are using. Whether it’s a Windows, Mac, iOS or Android operating system, you will still be able to bookmark this website.